設計服務簡介

當我們邁向深次微米的競技場時,對高性能和低成本IC的需求也不斷地增長。由於電晶體不斷地縮小導致設計複雜度的提高,符合「第一次Tape Out就成功」的目標已變得不易達成。倘若未能正確執行設計工作時,傳統的「一家公司包辦」的做法將導致公司耗費數百萬元重新Tape Out。更不用說因為延誤量產而造成商機的流失。

要成功Tape Out使IC或系統設計公司符合產品上市時間壓力的關鍵因素在於:

- 正確的設計流程和方法

- 可靠的制程技術準備就緒

- 矽晶圓驗證的IP和組件庫

EE Solutions在過去已經成功Tape Out超過800款的設計。自公司早期成立以來已有無數設計進入量產。成功完成這些設計需要本公司設計夥伴的各種來源支持。本公司正持續建立與EDA 廠商、IP/library廠商、和半導體晶圓代工廠的夥伴關係。我們堅信「分工」概念並積極地尋找新的夥伴以配合設計上不斷的挑戰。

本公司藉由和許多設計夥伴的共同合作而由不同的設計工具廠商中選擇最好的工具、由不同的IP廠商中找出最佳的IP、以及找出符合客戶設計需求的最佳半導體晶圓代工廠。本公司獨特之「混合」設計環境中所採用的工具,是來自于多個EDA廠商與內部所開發的工具,以便實現功率、雜訊、和晶片尺寸的最佳化。本公司已在TSMC、UMC、CSM、和SMIC等公司Tape Out我們的設計,以符合客戶的設計與業務需要。我們有大量適用於不同晶圓代工廠之多種制程技術的IP 。此外,由於本公司與設計夥伴的團隊合作,故能夠將我們最大的努力專注於提供完整的整合服務,使客戶能在多樣化應用領域中實現高性能的解決方案。

ASIC解決方案對客戶的價值

對客戶的價值

- 節省成本 (IC和BOM)

- 市場差異化 (獨特的解決方案)

- 客戶特定的解決方案 (非標準型IC或整合式IC解決方案)

- 產品保護 (非標準型ASIC的供應商)

- 產品的延伸 (靈活性)

- 安全的ASIC供應 (不必依靠IC供應商)

EES的服務種類

- 提供對應腳位的相容解決方案

- 提供多樣化IC整合解決方案

- 提供客制化IC解決方案

EES的差異化

- 提供系統和IC客戶通往大中華市場的管道

- 針對ASIC計畫而提供IP合作夥伴與設計夥伴的廣泛選擇

- 為了降低成本而提供臺灣與中國的測試和封裝選擇

- 內部IP開發的能力

- IO和記憶體開發的能力

- 先進設計技術與方法

- ESD

- RTL認證

- 階層式設計流程

- 頻率 / 功率方法

- 最佳的縮小技術 (GDS2GDS設計流程)

- 混合式設計流程

ASIC設計服務

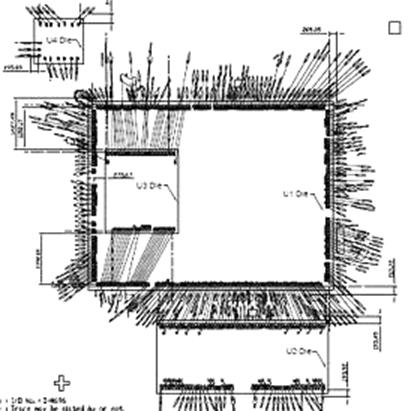

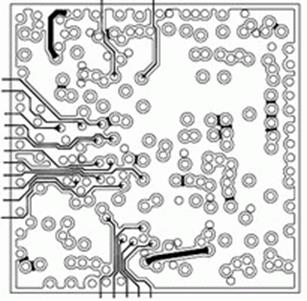

EES身為先進ASIC (包含ASIC 轉換服務) 的創新者,我們承諾實現完整的晶片設計:藉由與貴公司系統工程師與後勤管理的緊密合作,由設計建議起、經過IP設計與組態配置、晶片整合、FPGA的確認、一直到完整的後端制程、測試。我們有專業技術、智慧財產權(IP)、與系統層級的優勢,能將貴公司的設計版本整合至ASIC解決方案中,無論是單片式矽晶片或多晶片的單一封裝方式。EES的專長是在高可靠性、低功耗、與低成本的設計。本公司可整合IP庫與靈活的制程方法而實現成功且能夠負擔花費的系統單晶片 (SoC) 解決方案。

前端設計服務

- 架構規劃

- 系統層級模擬

- 邏輯設計與整合

- 先進封裝與原型產品

- 驗證

元件資料庫設計服務

- 設計規劃和原圖合成

- 低功耗設計

- 技術檔的開發與特性化

- 合成元件庫的萃取與模型開發

- Verilog格式

ASIC Analog IC

本公司提供各類型類比IP,並依照客戶需求,開發整合類比線路或特製功能的類比晶片。所設計的晶片涵蓋電源應用、類比訊號處理,高速傳輸訊號、時脈訊號產生、觸控訊號處理等。

- 電源應用:Battery Charger、DC-DC、DAC電壓電流供應器 等

- 模擬訊號處理:Sensor模擬訊號前端處理器 等

- 高速傳輸訊號:LVDS、 MIPI DPHY、 USB 2.0/3.0、 10/100 Ethernet PHY等介面晶片

- 訊脈產生器:各類頻率產生器

- 觸控訊號處理:電阻、電容、電磁觸控、指紋辨識晶片

SoC/平臺解決方案設計服務

本公司除了提供傳統的設計服務外,我們還建構了自有的解決方案平臺,不僅有能在工作站執行的設計資料庫,還有FPGA可供系統認證,能縮短客戶的整個設計週期。SOC設計是由許多的硬體區塊、制程核心、以及能結合整個系統的內嵌軟體所組成。本公司已經與部分EDA夥伴共同合作而完成了SOC設計與整合環境。本公司已開發出真正的平臺,可加速SOC開發的成果。本公司也完成了所謂BSP (開發板支持套件,Board Support Package) 的初級裝置驅動程式,能加速達成軟體發展的成果。本公司設計團隊中有經驗豐富的SOC設計師能指導貴公司建立SOC設計環境,並能根據需求而實現特殊化應用平臺,加速完成您的設計。

- SMART-USB / USB 2.0/3.0平臺

- 32-bit MCU + DSP平臺

- AIo T 平臺

- 32-bit SoC平臺 (including customized S/W & H/W base on ARM cortex –M series,RISC-V, MIPS …)

- Low power SoC platform

- FPGA Verification

由FPGA/RTL開始的設計

本公司能根據您的需求而由您的RTL/FPGA設計展開設計服務,並將其映射至對應的實體設計元件,最終能為您實現晶片產品和後勤管理。我們保證本公司的邏輯與實體設計團隊能同時確保IC在第一次Tape Out 時有完整的功能,使您可以執行原型測試並微調設計需求。本公司能根據您的業務與設計需求而提供下列建議:

- 選擇適當的晶圓代工廠、封裝和測試廠

- 選擇適當的制程技術

- 完成由合成到GDS的設計流程

- 後勤

由Netlist開始的設計

本公司根據您的需要而由您的netlist設計展開設計服務,最終能為您實現晶片產品和後勤管理。我們保證本公司的邏輯與實體設計團隊能同時確保IC在第一次Tape Out 時有完整的功能,使您可以執行原型測試並微調設計需求。本公司能根據您的業務與設計需求而提供下列建議:

- 選擇適當的封裝和測試廠

- DFT和APR

- 後勤

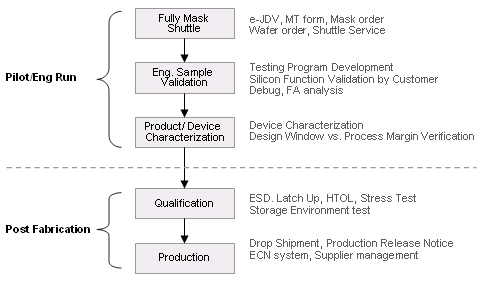

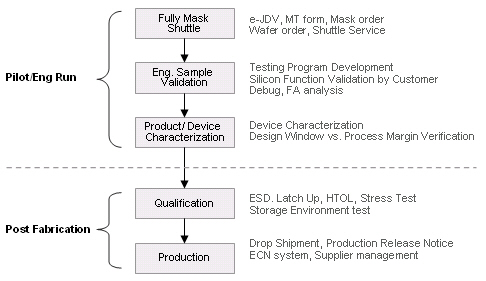

生產服務簡介

EE Solutions能提供廣泛的加值生產 / 製造工程服務,使客戶能從中選擇或補足內部無法取得的特殊性專門技術。EE Solutions的身分是作為您的生產夥伴而管理製造、封裝、測試、和交送。提供這類服務能使客戶接近EE Solutions內部的製造工程能力並且發揮本公司高端半導體供應鏈的影響力。這樣能使客戶得到許多好處,而且不會造成內部增加人力與製造作業所需要的花費與負擔。EE Solutions也能根據需要而提供完整系列的製造工程服務,其中包含封裝的選擇和設計、測試程式的開發、矽晶片驗證、故障分析、和新產品鑒定。

為何要選擇EES做為統包的合作夥伴?

- 提供具有成本競爭力的解決方案

- 提供在中國的設計 / 製造基礎工程

- 提供完善的供應鏈 (晶圓代工廠 / 封裝 / 測試 / 故障分析) - 成熟的量產統包流程

- 光罩tape out、晶圆制程、封装、测试程序开发、组件验证和特性分析 - 經驗豐富的供應鏈管理

- 專業的晶圓代工廠、封裝測試廠、與生產管控

- 廠商的資格認證流程、製造商直接出貨、在製品管控、時程管控

我們能提供哪些服務?

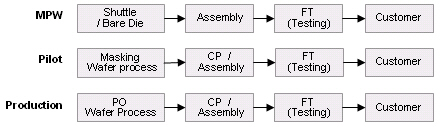

成熟的量產統包流程

晶圓製造

EE Solutions聯合世界級的晶圓代工廠提供完整的製造服務。EE Solutions的員工擁有多年的半導體製造經驗與產品工程經驗可提供至每一項保證。本公司和客戶因緊密合作所以能為客戶的設計選擇正確的制程和技術解決方案。要達成這項目標必須仔細地比較不同的晶圓代工廠、目的、與目標價格。本公司的製造工程人員能掌握最新的變化、並能跟隨各項既有以及新開發的技術,以便確保完整的選擇。

EE Solutions所提供的獨特服務包括送交快速、特殊特性的價廉IC原型產品是連晶圓代工廠都無法提供的服務。當前的晶圓代工廠會要求採購完整的光罩組,否則必須由多方案晶圓服務所構成,這樣一來就只能得到有限的封裝和測試選擇。由於多方案晶圓服務只能獲得有限數量的標準封裝,客戶必須同意採用裸晶片、未封裝與未測試的晶片。

EE Solutions提供完整整合的IC原型產品服務,範圍包含裸晶片到封裝,測試等所有工程服務事項。當客戶決定該選項時,EE Solutions會支援完整的封裝,其中包含客制化的封裝。此外,本公司可執行基本的電性和功能測試。

合作夥伴

|

|

封裝和組裝

由於元件幾何形狀的縮小,使半導體組裝過程變得更為複雜。隨著此複雜問題的難度提高就會增加微電子學的多樣性和複雜性,因此需要更多樣化的先進封裝類型。

EE Solutions理解選擇正確封裝解決方案的重要性,以便能符合各種設計的技術和成本限制。本公司的構裝工程師能將多年的封裝經驗導入設計週期中,並能提早進入設計週期。我們和客戶合作評估所能選擇的封裝 (BGA、Lead Frame、Flipchip、與SIP/MCM),針對設計的應用需要而採用最佳的封裝型式。本公司的工程師會與設計工程師緊密合作,確保基材設計能符合產品規格。

為瞭解決封裝上的挑戰,EE Solutions會確認與合作夥伴相關的需要,提供完整的封裝與測試解決方案與服務。此外,越接近這些高端合作夥伴,就能在雙方的工程小組間建立密不可分的工作氣氛,如此就能更迅速地對問題達成解決方案。我們的合作夥伴位在臺灣和中國,我們和ASE、SPIL、和TICP在封裝與組裝領域都有策略關係

合作夥伴

測試的開發

EE Solutions能為數位、類比、和記憶體區塊提供測試規劃與方法,並且和客戶合作選擇正確的測試平臺而優化成本。我們的工程師和臺灣的高端測試合作廠商有廣泛的合作經驗。本公司能提供乘載板和探針卡的方案,並能針對所有的主要平臺平臺 (Advantest、 Teradyne 、Cohu (LTX-credence) 、和Chorma) 提供測試程式的開發。我們有專用的測試圖樣轉換工具,能支援所有的主要平臺。EE Solutions富有經驗的工程師能根據所需要的腳位元元數、速率、和設計特性而決定最具成本效益的生產用測試機台。本公司所有的測試合作夥伴都位在臺灣,我們和ASE、SPIL、KYEC、Chipbond、 PAT、GT 、 YTEC都有合作關係,與這些廠商維持緊密關係將能更有效率的解決問題。

我們所提供的各類平臺能符合以下要件:

Successful Cases

|

Application |

Package Type |

Challenge/Character |

Tester |

|

Communication |

LQFP64 |

Analog Circuit |

Teradyne Catalyst |

|

4CDSP |

Parallel Testing |

||

|

(cost down version) |

|||

|

Communication |

PBGA |

Digital Circuit |

HP 83000 |

|

Controller-WCDMA |

High Pin Count |

||

|

Communication |

HSBGA |

Digital Circuit |

HP 83000 |

|

Controller-WCDMA |

High Pin Count |

||

|

System Controller |

CSBGA |

Digital Circuit |

Teradyne J750 |

|

High Pin Count |

|||

|

(cost down version) |

|||

|

System Controller |

HSBGA |

Digital Circuit |

Teradyne UltraFLEX |

|

High Pin Count/LVDS |

合作夥伴

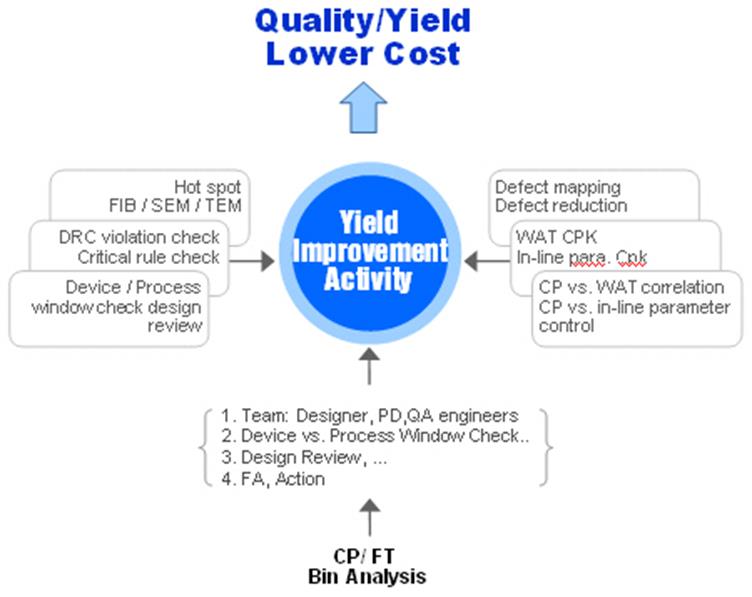

良率與故障分析

本公司產品工程小組的主要責任在於使每片晶圓的良率達到最高。為了讓我們的客戶獲得最佳的成本,EE Solutions會監督良率,並與晶圓代工廠以及封裝廠的工程師緊密合作,使良率達到最高。

EE Solutions能對完整的產品壽命週期提供全面性的品質服務。良率最佳化服務包含良率分析、corner lot的特性鑒定、與制程的重新導入。我們在驗證和除錯階段會提供基準點測量而協助客戶。EE Solutions提供的晶片和封裝認證包含老化測試、ESD、Latch up與高加速溫濕測試。

我們對新產品所提供的完整支援包含新產品認證、精密的故障分析與最佳化。

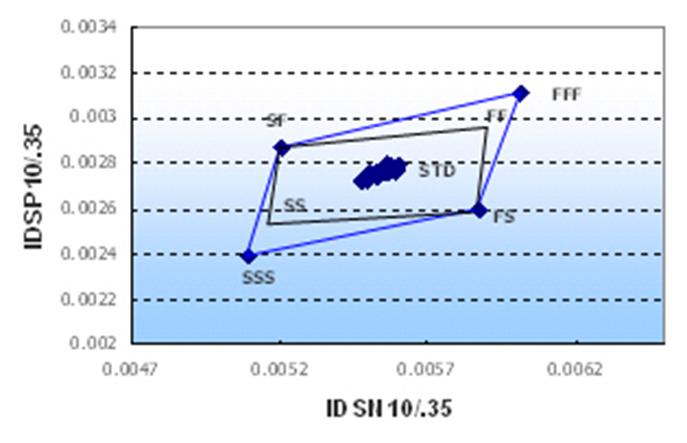

改善良率的能力

設計範圍對制程極限的檢查

產品可靠性的認證

- 客戶所要求的可靠性認證

- 認證規劃、取樣大小、專案

- 根據客戶的規劃

- 所參考的工業標準

- 封裝廠的參考資料 - 提供可靠性報告

- 資料分析與建議 - 提供故障分析與修正

整體的可靠性測試解決方案

|

Test Item |

Test Condition |

Readout (Hour or Cycle) |

Test Method |

|

Operating Life Test (OLT) |

Ta = 125℃, .3*Vcc |

168/500/1000 (HR) |

MIL-STD-750C |

|

Pressure Cooker Test (PCT) |

Ta = 121℃ |

48/96/168 (HR) |

MIL-STD-19500E |

|

Moisture Resistance |

Ta = 85℃ |

168/500/1000 (HR) |

MIL-STD-750C |

|

Temperature Humidity test (THT) |

Ta = 85℃ |

168/500/1000 (HR) |

JEDEC22-A101-B |

|

Temperature Humidity with Bias Test (THBT) |

Ta = 85℃ |

168/500/1000 (HR) |

JEDEC22-A101-B |

|

Thermal Shock Test (TST) |

-55℃/5mins to 150℃/5mins |

100 CYC |

MIL-STD-750C |

|

Temperature Cycling Test (TCT) |

-55℃/15mins to 125℃/15mins, |

500/1000 CYC |

MIL-STD-750C |

|

High Temperature Storage Life |

Ta = 150℃ |

168/500/1000 (HR) |

MIL-STD-750C |

整體的ESD、Latch-up測試解決方案

|

Test Item |

Test Condition |

Readout (Hour or Cycle) |

Test Method |

|

Electrostatic Discharge (ESD) |

Ta = 25℃, RH < 55%, |

VSS (±) |

JESD22-A114-B |

|

Latch-Up |

Ta = 25℃, |

+Voltage Trg –Voltage Trg |

EIA/JESD78 |

|

ELECTRO MIGRATION (EM) |

Follow JEDEC |

- |

>1.0 mA/um JESD63 |

|

Solder ability |

Ta = 215 ± 5℃ |

Dipping 5sec |

MIL-STD-750C |

故障分析的整體解決方案

- 電氣分析

- 波形記錄器、邏輯分析儀

- 信號產生器

- HP 4145, 4156 - 封裝分析

- X-ray, SAM

- De-cap, 幹式電漿蝕刻 - 漏電流分析

- EMMI, 液晶、亮點分析

- O Birch - 物理分析

- SEM, TEM, FIB, u-scope

故障分析

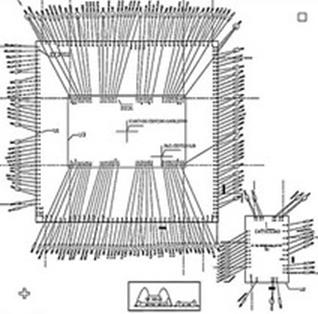

(1) X-ray分析

|

|

金線/ 金球分析 |

|

(2) De-Cap分析

|

|

保護層,上視圖 |

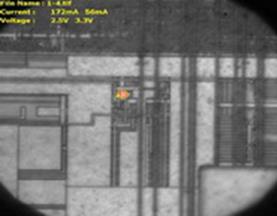

(3) 發光分析

|

|

|

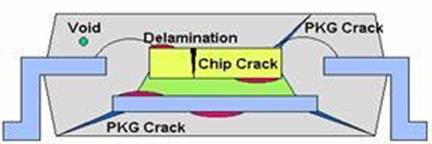

(4) SAM

|

|

|

後製作

倘若客戶已採購晶圓時,EE Solutions可完成IC的封裝、測試、與其它以上所列的綜合性服務。

結果是達成客制化晶片製造與交送的完整端對端解決方案,其中包含所有的後製作供應鏈管理。

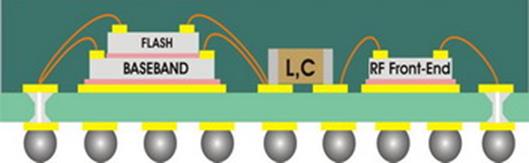

SIP解決方案

EES已為我們的客戶成功開發出SIP (MCM) 解決方案,能達到更高的元件性能、更小的封裝尺寸、以及更低的成本。各種不同封裝型式所採用的數種解決方案包括BGA、QFP、和Side-by-Side或堆疊晶片解決方案的WCSP。

|

Product |

Package Type |

Body Size |

KGD |

|

DTV |

TFBGA196 |

12*12 |

ASIC, AFE, SDRAM |

|

Security Camera |

TFBGA169 |

11*11 |

ASIC, Flash, SDRAM, Conroller |

|

Metrology |

QFP216 |

24*24 |

ASIC |

成功案例一:

- 應用:DTV

- 封裝型式:LFBGA 208、12mm*12 ^mm

- 晶片結構:三晶片堆疊 (Stack Dies + Side by Side)

- 晶片資訊:EES002 + eFlash + AFE

|

|

||

|

|

|

|

|

|

成功案例二:

- 應用:安全監控相機

- 封裝型式:LFBGA 169、11mm*11 ^mm

- 晶片結構:四晶片堆疊 (Stack Dies + Side by Side)

- 晶片資訊:EES002 + eFlash + SDRAM + 控制器

|

|

||

|

|

|

|

|

|

|

步驟一: |

提供晶片資訊 |

|

步驟二: |

簽訂合約 |

|

步驟三: |

開始基材設計 (二至四周) |

|

步驟四: |

工程樣品製作 |

|

步驟五: |

交貨 |

- EES經由最先進的方法而分擔設計品質的檢查,可確保最後晶片的最佳品質。

- 設計品質檢查包含:Code purification、netlist檢查、pin-ball的指定檢查、設計功率的計算、低功耗設計、cycle-base pattern轉換裝置。

- 可採用好幾種方式來確保最高品質與最低成本的晶片。

- 功率完整性流程:低功耗設計

- 信號完整性流程:信號完整性影響的處理

- 奈米設計流程:奈米物理 / 電氣特性的處理

- 光學縮小技術:以光學縮小化流程達到降低成本

- ESD品質檢查 / 設計:完整晶片ESD保護設計的方法

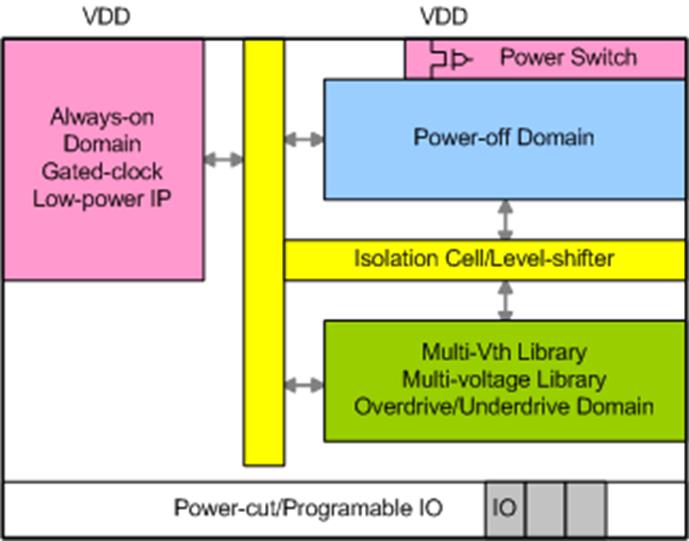

- EES的低功耗設計流程可提供使用者完整由前至後的方法,完成並驗證低功耗平臺。包含完成功率開關、多電源 / 多電壓、多Vt 元件庫、與閘控時鐘之低功耗設計方法的低功耗IP。

- 這些方法能有助於達成最低漏電流 / 待機 / 動態功耗。

- 功率開關法

- 漏電流: < 1.0 uA

- 性能不會降低

- 簡單的上電啟動流程

- 更好的IR結果 / 一致的IR控制 - 執行靜態IR分析、動態IR分析、SSO分析 / 預防

|

|

- 靜態IR / 動態IR分析

|

|

- SSO分析

|

|

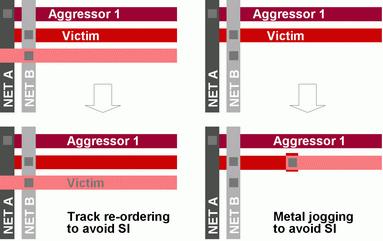

- EES信號完整性設計流程提供使用者完整的設計品質保證,確保奈米元件的物理 / 電氣效應。

- 高精確性的雜訊元件庫包含由spice模擬器所準備的AC/DC雜訊邊限。

- 時序分析能考慮由串音雜訊所引發的差異延遲。

- 經由「建構即成功」實現雜訊預防的流程

- 自動佈線最佳化能降低關鍵網路上的偶合電容

- 將負載置入犧牲性網路而降低耦合電容比

- 繞線re-order/metal jogging

- OCV (On Chip Variation)分析

- Multi-corner RC條件的處理

- 多模式限制時序最佳化

- 先進的可測試性設計:Scan Compression、at-speed Scan , Auto MBIST integration

光學縮小技術

EES為大晶片尺寸產品或高容量產品開發獨特的制程遷移流程。該流程使客戶能擁有「降低成本」的原始設計晶片,且不需要額外的人力來完成新設計。

ESD品質檢查 / 設計

- ESD保護設計

- 針對 I/O 單元提供優良的ESD保護設計法

- 優越的完整晶片ESD保護設計方法 - 多電源域設計

- 多類比 / 數位域設計

- ESD與電源 / 接地至信號單元距離之間的關聯性

- 高速應用的設計

- 耐高電壓 I/O 單元的設計

- 內嵌箝位元電路

- 良好的放電路徑

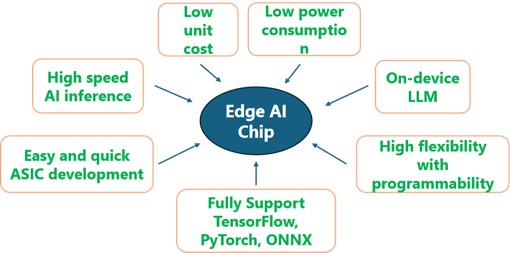

General Purpose Edge AI IP / TPU (GPTPU)

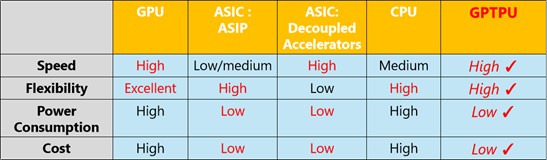

- GPTPU: By combining the ASAP platform with a novel tensor core, this solution delivers optimal tensor performance—especially for LLMs

- High Performance: GPTPU is highly optimized for processing large matrix in LLMs using on-chip tensor network, which can scale to Peta flops in one chip.

- Low Power Consumption: It can achieve a power efficiency of 8–20 TOPS per Watt using only a 22nm ASIC node, without relying on the most advanced process technology.

- Cost Efficient: The domain-specific accelerators in GPTPU achieve the same performance as GPU with at least 10x smaller area.

- Flexible/Programmable: ASAP architecture can reuse domain specific accelerators and shared accelerator Cache using flexible and low latency instruction scheduling. Therefore, it is programmable to adapt to improvements in AI models and switch to different models within the same AI domain—even after the chip being tape-out.

- GPTPU: Ideal for Edge AI

- GPTPU: Ideal for Edge AIASAP: It combines the advantages of ASIP and decoupled accelerators. It also allows designing advanced AI chips using high-level languages like C/C++ with quick turn-around development time.

- GPTPU: Combining ASAP platform with the novel tensor core enabling the optimum tensor performance, especially for LLM . High performance and flexibility but 10x higher power or cost efficiency than GPU.