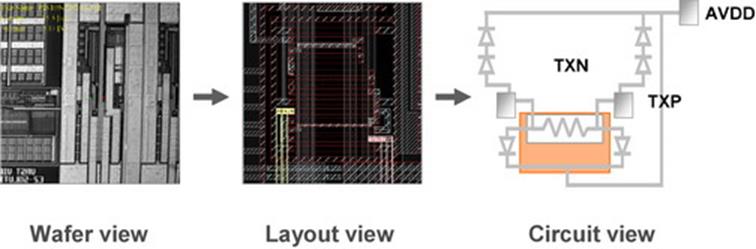

芯片设计服务

当我们迈向深次微米的竞技场时,对高性能和低成本IC的需求也不断地增长。由于晶体管不断地缩小导致设计复杂度的提高,符合「第一次Tape Out就成功」的目标已变得不易达成。倘若未能正确执行设计工作时,传统的「一家公司包办」的做法将导致公司耗费数百万元重新Tape Out。更不用说因为延误量产而造成商机的流失。

要成功Tape Out使IC或系统设计公司符合产品上市时间压力的关键因素在于:

- 正确的设计流程和方法

- 可靠的制程技术是否已准备就绪

- 是否可得到经过硅晶圆验证的IP和组件库

EE Solutions在过去已经成功Tape Out超过800款的设计。自公司早期成立以来已有无数设计进入量产。成功完成这些设计需要本公司设计伙伴的各种来源支持。本公司正持续建立与EDA 厂商、IP/library厂商、和半导体晶圆代工厂的伙伴关系。我们坚信「分工」概念并积极地寻找新的伙伴以配合设计上不断的挑战。

本公司藉由和许多设计伙伴的共同合作而由不同的设计工具厂商中选择最好的工具、由不同的IP厂商中找出最佳的IP、以及找出符合客户设计需求的最佳半导体晶圆代工厂。本公司独特之「混合」设计环境中所采用的工具,是来自于多个EDA厂商与内部所开发的工具,以便实现功率、噪声、和芯片尺寸的优化。本公司已在TSMC、UMC、CSM、和SMIC等公司Tape Out我们的设计,以符合客户的设计与业务需要。我们有大量适用于不同晶圆代工厂之多种制程技术的IP 。此外,由于本公司与设计伙伴的团队合作,故能够将我们最大的努力专注于提供完整的整合服务,使客户能在多样化应用领域中实现高性能的解决方案。

ASIC解决方案对客户的价值

对客户的价值

- 节省成本 (IC和BOM)

- 市场差异化 (独特的解决方案)

- 客户特定的解决方案 (非标准型IC或整合式IC解决方案)

- 产品保护 (非标准型ASIC的供货商)

- 产品的延伸 (灵活性)

- 安全的ASIC供应 (不必依靠IC供货商)

EES的服务种类

- 提供对应脚位的兼容解决方案

- 提供多样化IC整合解决方案

- 提供客制化IC解决方案

EES的差异化

- 提供系统和IC客户通往大中华市场的管道

- 针对ASIC计划而提供IP合作伙伴与设计伙伴的广泛选择

- 为了降低成本而提供台湾与中国的测试和封装选择

- 内部IP开发的能力

- IO和内存开发的能力

- 先进设计技术与方法

- ESD

- RTL认证

- 阶层式设计流程

- 频率 / 功率方法

- 最佳的缩小技术 (GDS2GDS设计流程)

- 混合式设计流程

一站式芯片定制服务

EES身为先进ASIC (包含ASIC 转换服务) 的创新者,我们承诺实现完整的芯片设计:藉由与贵公司系统工程师与后勤管理的紧密合作,由设计建议起、经过IP设计与组态配置、芯片整合、FPGA的确认、一直到完整的后端制程、测试。我们有专业技术、知识产权(IP)、与系统层级的优势,能将贵公司的设计版本整合至ASIC解决方案中,无论是单片式硅芯片或多芯片的单一封装方式。EES的专长是在高可靠性、低功耗、与低成本的设计。本公司可整合IP库与灵活的制程方法而实现成功且能够负担花费的系统单芯片 (SoC) 解决方案。

前端设计服务

- 架构规划

- 系统层级仿真

- 逻辑设计与整合

- 先进封装与原型产品

- 验证

组件数据库设计服务

- 设计规划和原图合成

- 低功耗设计

- 技术档的开发与特性化

- 合成组件库的萃取与模型开发

- Verilog格式

ASIC Analog IC

本公司提供各类型模拟IP,并依照客户需求,开发整合模拟线或特制功能的模拟芯片。所设计的芯片涵盖电源应用、模拟讯号处理,高速传输讯号、频率讯号产生、触控讯号处理等。

- 电源应用:Battery Charger、DC-DC、DAC电压电流供应器 等

- 仿真讯号处理:Sensor仿真讯号前端处理器 等

- 高速传输讯号:LVDS、 MIPI DPHY、 USB 2.0/3.0、 10/100 Ethernet PHY等接口芯片

- 讯脉产生器:各类频率产生器

- 触控讯号处理:电阻、电容、电磁触控、指纹辨识芯片

SoC/平台解决方案设计服务

本公司除了提供传统的设计服务外,我们还建构了自有的解决方案平台,不仅有能在工作站执行的设计数据库,还有FPGA可供系统认证,能缩短客户的整个设计周期。SOC设计是由许多的硬件区块、制程核心、以及能结合整个系统的内嵌软件所组成。本公司已经与部分EDA伙伴共同合作而完成了SOC设计与整合环境。本公司已开发出真正的平台,可加速SOC开发的成果。本公司也完成了所谓BSP (开发板支持套件,Board Support Package) 的初级设备驱动器,能加速达成软件开发的成果。本公司设计团队中有经验丰富的SOC设计师能指导贵公司建立SOC设计环境,并能根据需求而实现特殊化应用平台,加速完成您的设计。

- SMART-USB / USB 2.0/3.0平台

- 32-bit MCU + DSP平台

- AIo T 平台

- 32-bit SoC平台 (including customized S/W & H/W base on ARM cortex –M series,RISC-V, MIPS …)

- Low power SoC platform

- FPGA Verification

由FPGA/RTL开始的设计

本公司能根据您的需求而由您的RTL/FPGA设计展开设计服务,并将其映像至对应的实体设计组件,最终能为您实现芯片产品和后勤管理。我们保证本公司的逻辑与实体设计团队能同时确保IC在第一次Tape Out 时有完整的功能,使您可以执行原型测试并微调设计需求。本公司能根据您的业务与设计需求而提供下列建议:

- 选择适当的晶圆代工厂、封装和测试厂

- 选择适当的制程技术

- 完成由合成到GDS的设计流程

- 后勤

由Netlist开始的设计

本公司根据您的需要而由您的netlist设计展开设计服务,最终能为您实现芯片产品和后勤管理。我们保证本公司的逻辑与实体设计团队能同时确保IC在第一次Tape Out 时有完整的功能,使您可以执行原型测试并微调设计需求。本公司能根据您的业务与设计需求而提供下列建议:

- 选择适当的封装和测试厂

- DFT和APR

- 后勤

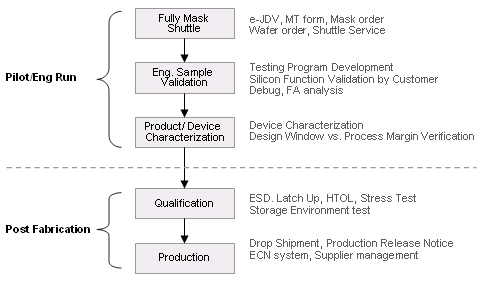

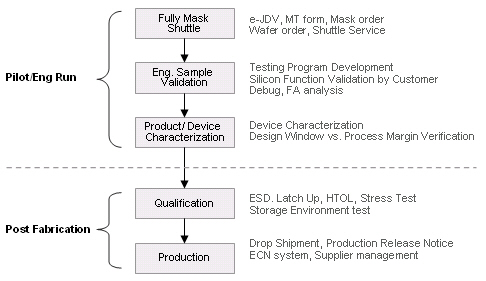

生产服务简介

EE Solutions能提供广泛的加值生产 / 制造工程服务,使客户能从中选择或补足内部无法取得的特殊性专门技术。EE Solutions的身分是作为您的生产伙伴而管理制造、封装、测试、和交送。提供这类服务能使客户接近EE Solutions内部的制造工程能力并且发挥本公司高端半导体供应链的影响力。这样能使客户得到许多好处,而且不会造成内部增加人力与制造作业所需要的花费与负担。EE Solutions也能根据需要而提供完整系列的制造工程服务,其中包含封装的选择和设计、测试程序的开发、硅芯片验证、故障分析、和新产品鉴定。

为何要选择EES做为统包的合作伙伴?

- 提供具有成本竞争力的解决方案

- 提供在中国的设计 / 制造基础工程

- 提供完善的供应链 (晶圆代工厂 / 封装 / 测试 / 故障分析) - 成熟的量产统包流程

- 光罩tape out、晶圆制程、封装、测试程序开发、组件验证和特性分析。 - 经验丰富的供应链管理

- 专业的晶圆代工厂、封装测试厂、与生产管控

- 厂商的资格认证流程、制造商直接出货、在制品管控、时程管控

我们能提供哪些服务?

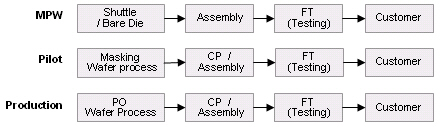

成熟的量产统包流程

晶圆制造

EE Solutions联合世界级的晶圆代工厂提供完整的制造服务。EE Solutions的员工拥有多年的半导体制造经验与产品工程经验可提供至每一项保证。本公司和客户因紧密合作所以能为客户的设计选择正确的制程和技术解决方案。要达成这项目标必须仔细地比较不同的晶圆代工厂、目的、与目标价格。本公司的制造工程人员能掌握最新的变化、并能跟随各项既有以及新开发的技术,以便确保完整的选择。

EE Solutions所提供的独特服务包括送交快速、特殊特性的价廉IC原型产品是连晶圆代工厂都无法提供的服务。当前的晶圆代工厂会要求采购完整的光罩组,否则必须由多方案晶圆服务所构成,这样一来就只能得到有限的封装和测试选择。由于多方案晶圆服务只能获得有限数量的标准封装,客户必须同意采用裸芯片、未封装与未测试的芯片。

EE Solutions提供完整整合的IC原型产品服务,范围包含裸芯片到封装,测试等所有工程服务事项。当客户决定该选项时,EE Solutions会支持完整的封装,其中包含客制化的封装。此外,本公司可执行基本的电性和功能测试。

合作伙伴

|

|

封装和组装

由于组件几何形状的缩小,使半导体组装过程变得更为复杂。随着此复杂问题的难度提高就会增加微电子学的多样性和复杂性,因此需要更多样化的先进封装类型。

EE Solutions理解选择正确封装解决方案的重要性,以便能符合各种设计的技术和成本限制。本公司的构装工程师能将多年的封装经验导入设计周期中,并能提早进入设计周期。我们和客户合作评估所能选择的封装 (BGA、Lead Frame、Flipchip、与SIP/MCM),针对设计的应用需要而采用最佳的封装型式。本公司的工程师会与设计工程师紧密合作,确保基材设计能符合产品规格。

为了解决封装上的挑战,EE Solutions会确认与合作伙伴相关的需要,提供完整的封装与测试解决方案与服务。此外,越接近这些高端合作伙伴,就能在双方的工程小组间建立密不可分的工作气氛,如此就能更迅速地对问题达成解决方案。我们的合作伙伴位在台湾和中国,我们和ASE、SPIL、和TICP在封装与组装领域都有策略关系

合作伙伴

测试的开发

EE Solutions能为数字、模拟、和内存区块提供测试规划与方法,并且和客户合作选择正确的测试平台而优化成本。我们的工程师和台湾的高端测试合作厂商有广泛的合作经验。本公司能提供乘载板和探针卡的方案,并能针对所有的主要平台平台 (Advantest、 Teradyne 、Cohu (LTX-credence) 、和Chorma) 提供测试程序的开发。我们有专用的测试图样转换工具,能支持所有的主要平台。EE Solutions富有经验的工程师能根据所需要的脚位元元数、速率、和设计特性而决定最具成本效益的生产用测试机台。本公司所有的测试合作伙伴都位在台湾,我们和ASE、SPIL、KYEC、Chipbond、PAT、GT、YTEC都有合作关系,与这些厂商维持紧密关系将能更有效率的解决问题。

我们所提供的各类平台能符合以下要件:

Successful Cases

|

Application |

Package Type |

Challenge/Character |

Tester |

|

Communication |

LQFP64 |

Analog Circuit |

Teradyne Catalyst |

|

4CDSP |

Parallel Testing |

||

|

(cost down version) |

|||

|

Communication |

PBGA |

Digital Circuit |

HP 83000 |

|

Controller-WCDMA |

High Pin Count |

||

|

Communication |

HSBGA |

Digital Circuit |

HP 83000 |

|

Controller-WCDMA |

High Pin Count |

||

|

System Controller |

CSBGA |

Digital Circuit |

Teradyne J750 |

|

High Pin Count |

|||

|

(cost down version) |

|||

|

System Controller |

HSBGA |

Digital Circuit |

Teradyne UltraFLEX |

|

High Pin Count/LVDS |

合作伙伴

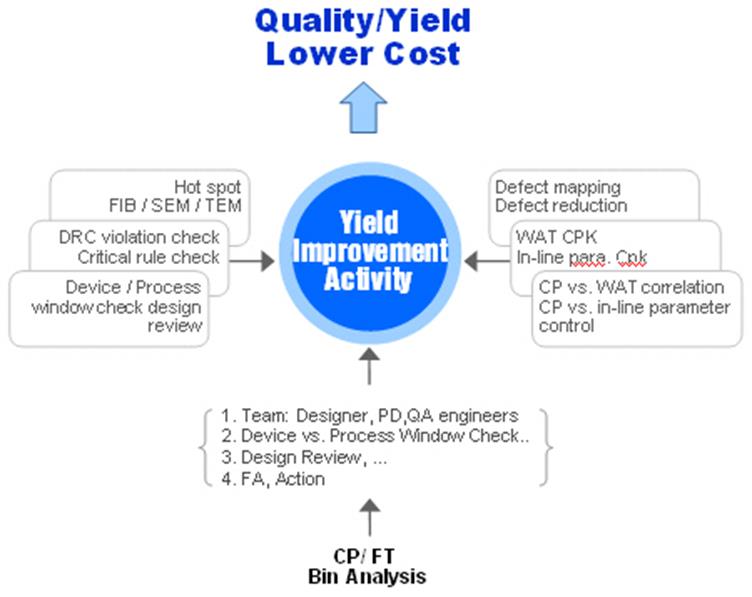

良率与故障分析

本公司产品工程小组的主要责任在于使每片晶圆的良率达到最高。为了让我们的客户获得最佳的成本,EE Solutions会监督良率,并与晶圆代工厂以及封装厂的工程师紧密合作,使良率达到最高。

EE Solutions能对完整的产品寿命周期提供全面性的质量服务。良率优化服务包含良率分析、corner lot的特性鉴定、与制程的重新导入。我们在验证和除错阶段会提供基准点测量而协助客户。EE Solutions提供的芯片和封装认证包含老化测试、ESD、Latch up与高加速温湿测试。

我们对新产品所提供的完整支持包含新产品认证、精密的故障分析与优化。

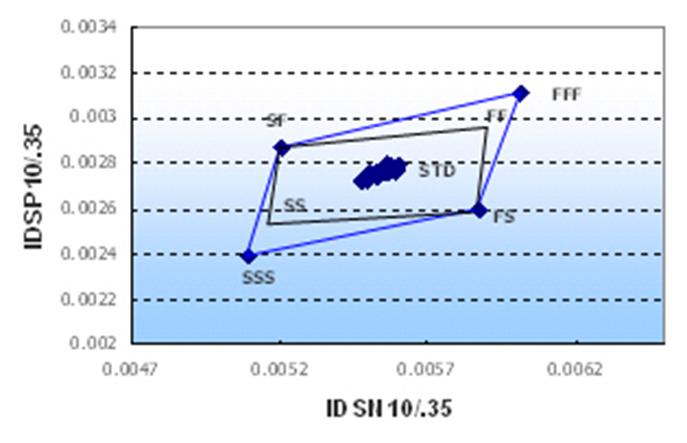

改善良率的能力

设计范围对制程极限的检查

产品可靠性的认证

- 客户所要求的可靠性认证

- 认证规划、取样大小、项目

- 根据客户的规划

- 所参考的工业标准

- 封装厂的参考数据 - 提供可靠性报告

- 数据分析与建议 - 提供故障分析与修正

整体的可靠性测试解决方案

|

Test Item |

Test Condition |

Readout (Hour or Cycle) |

Test Method |

|

Operating Life Test (OLT) |

Ta = 125℃, .3*Vcc |

168/500/1000 (HR) |

MIL-STD-750C |

|

Pressure Cooker Test (PCT) |

Ta = 121℃ |

48/96/168 (HR) |

MIL-STD-19500E |

|

Moisture Resistance |

Ta = 85℃ |

168/500/1000 (HR) |

MIL-STD-750C |

|

Temperature Humidity test (THT) |

Ta = 85℃ |

168/500/1000 (HR) |

JEDEC22-A101-B |

|

Temperature Humidity with Bias Test (THBT) |

Ta = 85℃ |

168/500/1000 (HR) |

JEDEC22-A101-B |

|

Thermal Shock Test (TST) |

-55℃/5mins to 150℃/5mins |

100 CYC |

MIL-STD-750C |

|

Temperature Cycling Test (TCT) |

-55℃/15mins to 125℃/15mins, |

500/1000 CYC |

MIL-STD-750C |

|

High Temperature Storage Life |

Ta = 150℃ |

168/500/1000 (HR) |

MIL-STD-750C |

整体的ESD、Latch-up测试解决方案

|

Test Item |

Test Condition |

Readout (Hour or Cycle) |

Test Method |

|

Electrostatic Discharge (ESD) |

Ta = 25℃, RH < 55%, |

VSS (±) |

JESD22-A114-B |

|

Latch-Up |

Ta = 25℃, |

+Voltage Trg –Voltage Trg |

EIA/JESD78 |

|

ELECTRO MIGRATION (EM) |

Follow JEDEC |

- |

>1.0 mA/um JESD63 |

|

Solder ability |

Ta = 215 ± 5℃ |

Dipping 5sec |

MIL-STD-750C |

故障分析的整体解决方案

- 电气分析

- 波形记录器、逻辑分析仪

- 信号产生器

- HP 4145, 4156 - 封装分析

- X-ray, SAM

- De-cap, 干式电浆蚀刻 - 漏电流分析

- EMMI, 液晶、亮点分析

- O Birch - 物理分析

- SEM, TEM, FIB, u-scope

故障分析

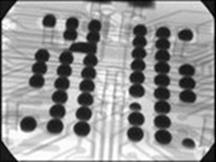

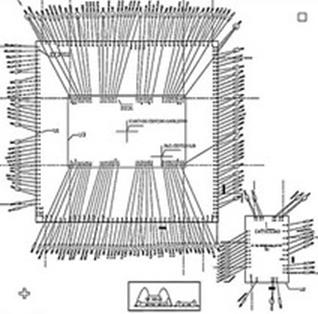

(1) X-ray分析

|

|

金线/ 金球分析 |

|

(2) De-Cap分析

|

|

保护层,上视图 |

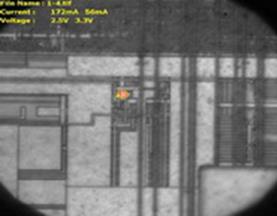

(3) 发光分析

|

|

|

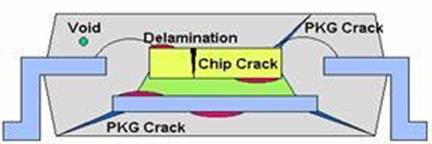

(4) SAM

|

|

|

后制作

倘若客户已采购晶圆时,EE Solutions可完成IC的封装、测试、与其它以上所列的综合性服务。

结果是达成客制化芯片制造与交送的完整端对端解决方案,其中包含所有的后制作供应链管理。

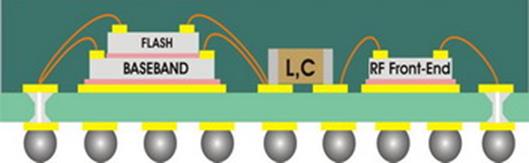

SIP解决方案

EES已为我们的客户成功开发出SIP (MCM) 解决方案,能达到更高的组件性能、更小的封装尺寸、以及更低的成本。各种不同封装型式所采用的数种解决方案包括BGA、QFP、和Side-by-Side或堆栈芯片解决方案的WCSP。

|

Product |

Package Type |

Body Size |

KGD |

|

DTV |

TFBGA196 |

12*12 |

ASIC, AFE, SDRAM |

|

Security Camera |

TFBGA169 |

11*11 |

ASIC, Flash, SDRAM, Conroller |

|

Metrology |

QFP216 |

24*24 |

ASIC |

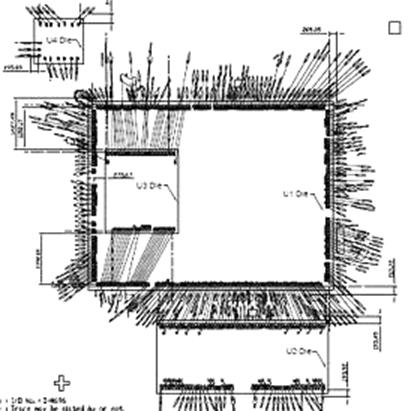

成功案例一:

- 应用:DTV

- 封装型式:LFBGA 208、12mm*12 ^mm

- 芯片结构:三芯片堆栈 (Stack Dies + Side by Side)

- 芯片信息:EES002 + eFlash + AFE

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

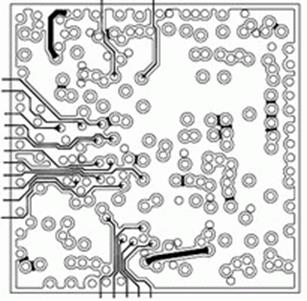

成功案例二:

- 应用:安全监控相机

- 封装型式:LFBGA 169、11mm*11 ^mm

- 芯片结构:四芯片堆栈 (Stack Dies + Side by Side)

- 芯片信息:EES002 + eFlash + SDRAM + 控制器

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

步骤一: |

提供芯片信息 |

|

步骤二: |

签订合约 |

|

步骤三: |

开始基材设计 (二至四周) |

|

步骤四: |

工程样品制作 |

|

步骤五: |

交货 |

- EES经由最先进的方法而分担设计质量的检查,可确保最后芯片的最佳质量。

- 设计质量检查包含:Code purification、netlist检查、pin-ball的指定检查、设计功率的计算、低功耗设计、cycle-base pattern转换装置。

- 可采用好几种方式来确保最高质量与最低成本的芯片。

- 功率完整性流程:低功耗设计

- 信号完整性流程:信号完整性影响的处理

- 奈米设计流程:奈米物理 / 电气特性的处理

- 光学缩小技术:以光学缩小化流程达到降低成本

- ESD质量检查 / 设计:完整芯片ESD保护设计的方法

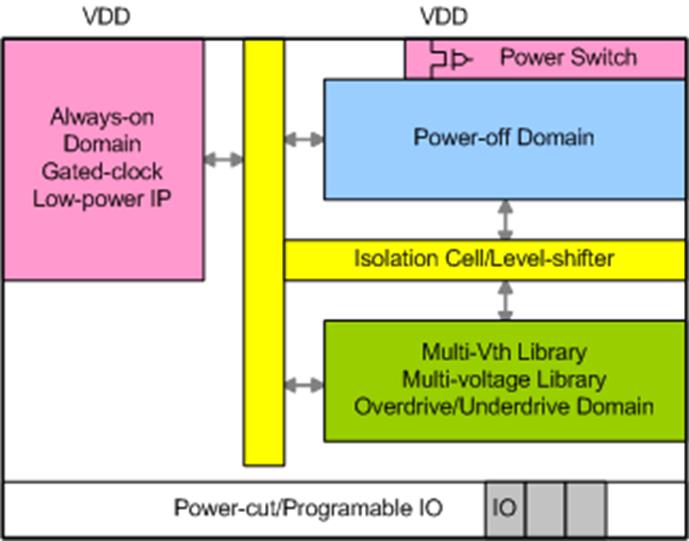

- EES的低功耗设计流程可提供用户完整由前至后的方法,完成并验证低功耗平台。包含完成功率开关、多电源 / 多电压、多Vt 组件库、与闸控时钟之低功耗设计方法的低功耗IP。

- 这些方法能有助于达成最低漏电流 / 待机 / 动态功耗。

- 功率开关法

- 漏电流: < 1.0 uA

- 性能不会降低

- 简单的上电启动流程

- 更好的IR结果 / 一致的IR控制 - 执行静态IR分析、动态IR分析、SSO分析 / 预防

|

|

|

- 静态IR / 动态IR分析

|

|

|

- SSO分析

|

|

|

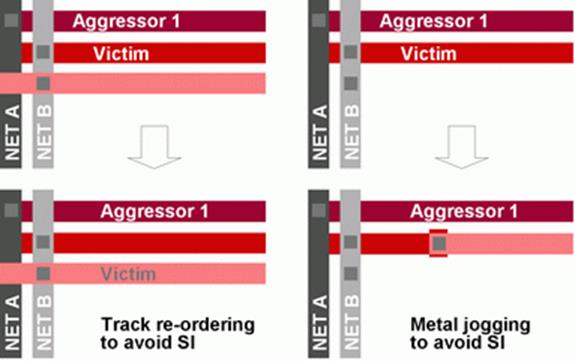

- EES信号完整性设计流程提供用户完整的设计质量保证,确保奈米组件的物理 / 电气效应。

- 高精确性的噪声组件库包含由spice仿真器所准备的AC/DC噪声边限。

- 时序分析能考虑由串音噪声所引发的差异延迟。

- 经由「建构即成功」实现噪声预防的流程

- 自动布线优化能降低关键网络上的偶合电容

- 将负载置入牺牲性网络而降低耦合电容比

- 绕线re-order/metal jogging

- OCV (On Chip Variation)分析

- Multi-corner RC条件的处理

- 多模式限制时序优化

- 先进的可测试性设计:Scan Compression、at-speed Scan , Auto MBIST integration

光学缩小技术

EES为大芯片尺寸产品或高容量产品开发独特的制程迁移流程。该流程使客户能拥有「降低成本」的原始设计芯片,且不需要额外的人力来完成新设计。

ESD质量检查 / 设计

- ESD保护设计

- 针对 I/O 单元提供优良的ESD保护设计法

- 优越的完整芯片ESD保护设计方法 - 多电源域设计

- 多模拟 / 数字域设计

- ESD与电源 / 接地至信号单元距离之间的关联性

- 高速应用的设计

- 耐高电压 I/O 单元的设计

- 内嵌箝位电路

- 良好的放电路径